引言

本文主要探讨了CIRCT的创立动机、发展历程以及MLIR的起源,特别是Chris Lattner博士在2021年ASPLOS学术会议上分享的关于“软硬件协同设计时代的编译器设计黄金时代”的主题。接着,通过简单的例子,分析了MLIR与CIRCT如何实现软硬件协同设计的过程。最后,在文章结尾表明,CIRCT项目致力于将MLIR的软件开发方法应用于硬件设计,旨在打破传统开源EDA工具之间的碎片化,实现更高效、更统一的设计流程,以满足未来对定制化硬件设计的需求。

CIRCT项目创立动机

CIRCT(Circuit IR Compilers and Tools)项目是一个基于MLIR框架硬件编译器框架,旨在将开源的EDA工具的功能整合到同一框架中,以提供灵活可配置的基础设施,并支持多种硬件设计模式。该项目于2021年在ASPLOS学术会议上由Chris Lattner分享主题为“软硬件协同设计时代的编译器设计黄金时代”一文中首次被提出。 CIRCT项目的立项动机源于对当前开源EDA工具碎片化现状的深刻洞察,以及对计算机体系结构发展趋势的前瞻性思考。在EDA行业,虽然存在许多出色的开源工具,如综合工具Yosys、仿真工具Verilator、布局布线工具nextpnr和OpenROAD,以及基于Python的硬件设计工具Magma等。但是这些开源EDA工具通常独自形成生态,各自发展,在语言、接口和数据格式上缺乏统一的标准,加之在多年发展中积累了复杂的历史代码和架构,使得各个工具之间难以集成和协同,从而造成当今开源EDA工具碎片化现状。此外,随着摩尔定律和登纳德缩放定律的终结,未来的计算机体系结构将更加注重能效比、并行处理能力以及对新兴技术的支持。 在这种背景下,CIRCT项目的目标是建立一个统一的开源EDA平台,借鉴RISC-V指令集的开放性、模块化和可扩展性,并结合LLVM/MLIR软件开发方法,以满足未来计算机体系结构的发展需求,解决开源EDA工具的碎片化现状,加速加速器(DSA)设计,推动硬件设计工具的革新。通过构建一个模块化、可扩展的平台,CIRCT希望能够促进硬件开发社区的协作与创新,从而提升整体设计效率和质量。该项目不仅为硬件设计提供了一种新的方法论,也为未来的开源硬件生态系统奠定了基础。

CIRCT发展历程

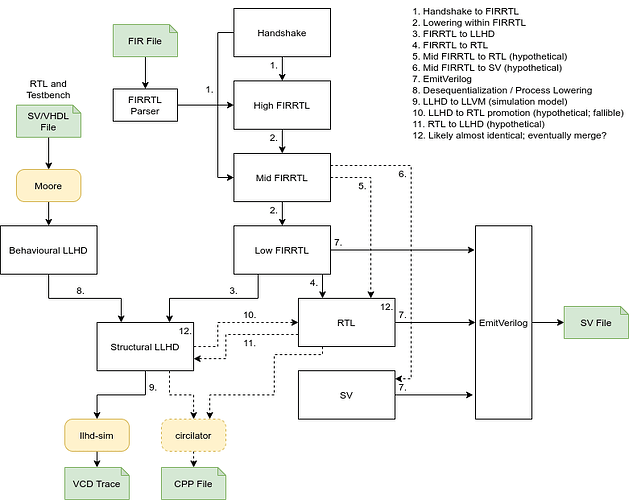

在2021年1月CIRCT项目发展初期,整个项目结构如下图所示:

图1:2021年CIRCT方言转换图

此时,RTL方言层代表着Comb(表示组合电路),Seq(表示时序电路),HW(表示SV中结构化的特性)。

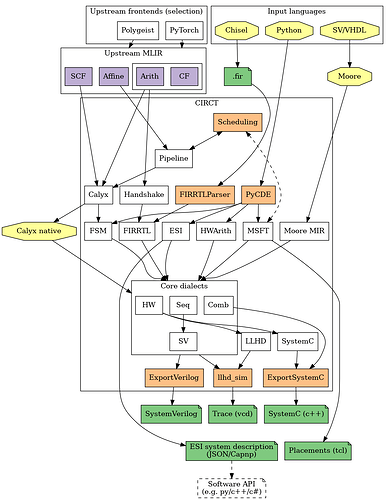

在2022年8月,CIRCT项目引入了HWArith、SystemC以及Moore MIR等新方言,并新增了ExportSystemC功能。这些新增方言显著增强了项目的灵活性,使得Python和SystemVerilog/VHDL这两条技术路线能够进行更深入的优化。同时,新增的ExportSystemC功能允许从硬件代码生成C++代码。这些改进为开发者提供了更多工具和选项,从而在设计和实现过程中实现更高效的优化。如下图所示:

图2:2022年CIRCT方言转换图

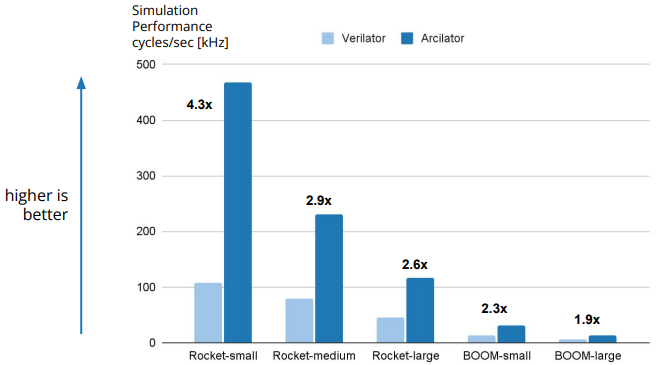

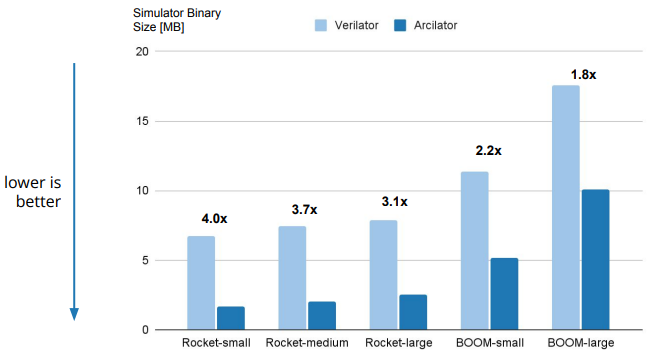

在2023年LLVM峰会期间,SiFive公司分享了题为“快速和周期精确的CIRCT硬件仿真器:Arcilator(原名Circilator)”的演讲。此次演讲中,重点对Rocket-small、Rocket-medium、Rocket-large以及BOOM-small和BOOM-large这两个RISC-V核进行单线程仿真。数据显示,当对Rocket-small进行基准测试时,Arcilator的仿真速度比Verilator快4.3倍;即便是在对BOOM-large进行基准测试时,Arcilator仍然展现出优势,其速度是Verilator的1.9倍。此外,在仿真Rocket-small时,Arcilator生成的二进制文件大小比Verilator小4倍,而对应的BOOM-large也比Verilator小1.8倍。这些结果表明,Arcilator在性能和效率上均优于传统的仿真工具,为硬件设计提供了更为高效的解决方案。图3、图4是Arcilator与Verilator数据对比图:

图3:Arcilator与Verilator仿真性能对比

图4:Arcilator与Verilator二进制仿真文件大小对比

这种显著的性能提升不仅彰显了Arcilator作为硬件仿真工具的潜力,也验证了CIRCT采用多层级中间表示的可行性。

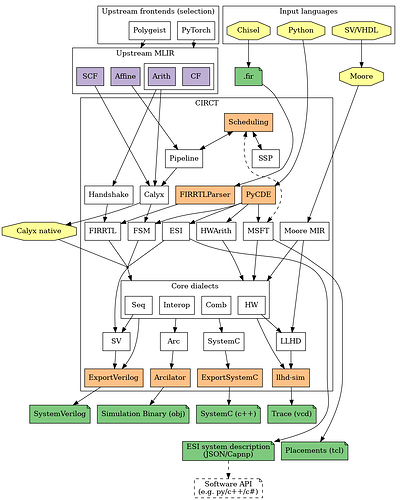

但随着Arcilator的出现,作为事件驱动的llhd-sim逐渐被边缘化,Arcilator迅速成为CIRCT项目中的主流仿真器。此外,同年CIRCT还引入了多个新方言,包括用于信号追踪的Debug方言、用于验证的Verify方言、表示线性时序逻辑序列和属性的LTL方言(SVA),以及用于形式化验证的SMT方言等。这些新增方言进一步增强了CIRCT在硬件设计领域的能力,为开发者提供了更丰富的工具和选项。(这些调试、验证相关的方言并未展示在CIRCT方言转换图中,而是分散在不同的方言中,以形成验证流。)在增加了Arcilator仿真器之后,CIRCT形成了新的方言和流程,如下图所示:

图5:新增Arcilator仿真器的方言转换图

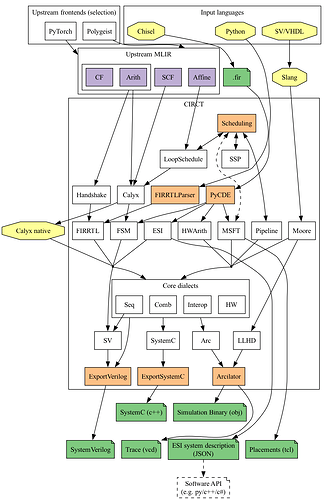

兆松自2023年7月起加入CIRCT社区,持续为CIRCT项目的发展贡献力量。兆松发现并看好slang这一SystemVerilog前端编译器,随后开始尝试将slang作为CIRCT的外部库引入,并在SystemVerilog技术路线方面进行深入探索。兆松扩展了Moore方言,以支持更多SystemVerilog特性,特别是基于IEEE Std 1800-2017标准的特性。这一变更使得原本的Moore前端编译器被slang所替代。 在2024年3月,兆松在CIRCT周会上分享了SystemVerilog技术路线的特性支持情况,指出在Moore层已支持绝大部分可综合的SystemVerilog特性。随后,CIRCT社区决定移除 llhd-sim,不再使用,但把部分LLHD方言的功能保留并融入了Arcilator。功能调整如下图所示:

图6:2024年CIRCT方言转换图

这些调整标志着CIRCT在硬件设计领域的进一步发展,展示了其在技术整合和优化方面的持续努力。通过这些变更,CIRCT不仅提升了工具链的灵活性和性能,还为开发者提供了更强大的功能支持,推动了开源EDA工具生态的创新与进步。

从CIRCT的发展历程来看,CIRCT社区在不到三年的时间里,已向工业界交付了一份出色的成果:在单线程仿真性能方面,Arcilator的表现优于Verilator,展示了其卓越的效率;此外,CIRCT项目还支持高层级综合、形式化验证、C++/SV代码输出、布局布线,以及出色的错误定位功能等。随着 SystemVerilog 技术路线的持续推进,CIRCT将变得愈加强大。未来,诸如逻辑综合等目前尚缺失的功能也将逐步得到完善和支持。

MLIR起源

MLIR(Multi-Level Intermediate Representation)项目于2018年由谷歌团队发起,旨在解决软件碎片化问题,提高对异构硬件的编译效率,并降低构建领域特定编译器的成本,同时帮助将现有的编译器连接在一起。作为LLVM下的一个子项目,MLIR的方法学是通过提供一个可重用、可扩展和多层级中间表示的编译器基础设施,支持不同的编程模型和硬件架构,使编译器能够在不同层级上进行优化和转换,从而更高效地处理复杂的计算任务。 MLIR广泛应用于多个领域,包括高性能计算、机器学习、量子计算、代码生成及硬件综合等,成为现代编译器技术的重要组成部分。其灵活性和扩展性使得开发者能够利用MLIR来优化各种计算任务,从而提升性能并降低开发成本。随着技术的发展,MLIR将继续推动编译器基础设施的创新,为未来的计算需求提供强有力的支持。

基于MLIR的软硬件协同设计

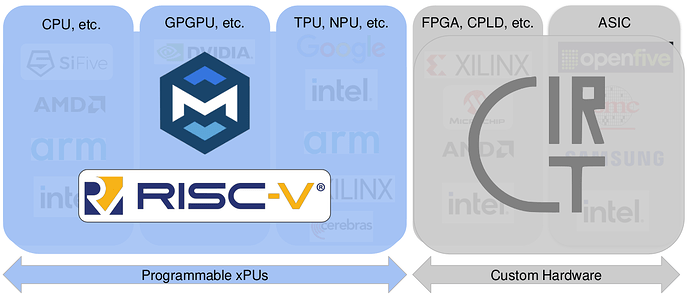

在“软硬件协同设计时代的编译器设计黄金时代”一文中,Chris Lattner博士提到的“Lots of players!” 反映了当前硬件市场在兼容性和开放性方面存在不足。具体而言,CPU、GPGPU、xPU、FPGA、ASIC等多种架构和厂商之间缺乏统一的编译框架,这种碎片化现状给开发者和研究人员带来了诸多挑战,因为不同的硬件平台通常需要独特的编译和优化策略。

为了解决软件编译工具栈的碎片化问题,并加速加速器的编译,文中提出RISC-V+MLIR结合。这一组合的优势体现在以下几个方面:

-

通过将有限的编译工程资源集中在一个更大的中心上,促进编译器生态系统的创新,尤其是在编程模型和硬件方面;

-

实现“前端+后端”的可扩展性,使得整个编译器生态系统能够更好的适应不同的需求和平台;

-

通过减少工具之间的碎片化,增加模块化概念,使得开发者可以重用已有的设计,仅专注于技术栈中差异化的部分。

在同样面临碎片化问题的EDA领域,文中提到了CIRCT项目,在CIRCT创立动机一节中已经探讨过,这里就不做额外介绍了。 为满足未来算力需求并加速定制化硬件设计,解决碎片化问题显得尤为紧迫。RISC-V & MLIR + CIRCT的结合,是Chris Lattner博士对这一挑战的深刻见解。如下图所示:

图7:MLIR & RISC-V + CIRCT解决软硬件协同设计

开发者可以利用RISC-V的可扩展性,根据具体需求灵活地定制硬件;通过MLIR中的统一编译流程,将软件逻辑自动生成机器指令,以及通过HLS将硬件逻辑转换成CIRCT中方言。这一流程不仅支持额外的优化和功能验证,还能实现定制化硬件设计的快速落地。

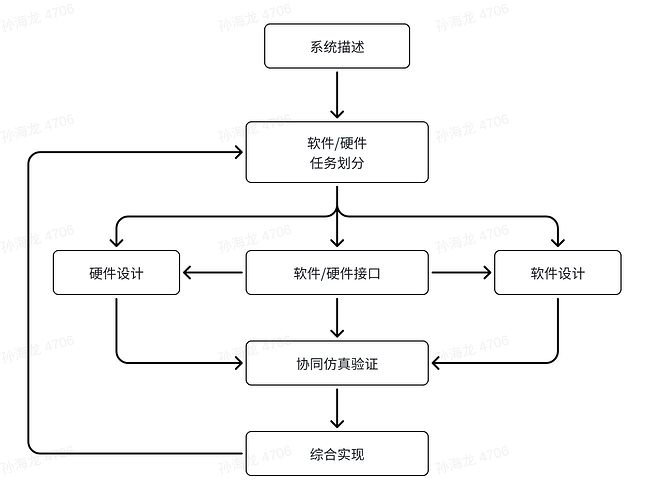

软硬件协同设计概述

软硬件协同设计(Hardware Software Co-design)是指在系统芯片开发过程中,软件与硬件共同定义和开发的过程,解决随着系统复杂性增加而产生的设计挑战。这一方法学自20世纪90年代初期开始发展,并迅速应用于系统芯片设计中。许多现代EDA工具和平台,如ARM公司的RVDS、Cypress公司的PSoC Creator IDE和Synopsys公司的Virtual Platform,均支持这种设计方法。

软硬件协同设计的核心概念如下:

-

共同开发:在软硬件协同设计中,软件和硬件的开发过程是并行进行的,而非传统上分别独立开发。这种交互式设计方式允许在每个阶段进行验证和调整,从而提高系统的整体性能和可靠性。

-

功能划分:设计者需要在系统层面上进行功能划分,确定哪些功能模块采用硬件实现,哪些采用软件实现。这一划分不仅考虑技术因素,还需评估开发时间、成本和市场资源等多方面因素。

-

仿真验证:通过软硬件协同仿真验证,可以在设计早期发现潜在问题,避免在后期整合时产生高昂的修改成本。此过程确保了设计的正确性和性能评估。

-

综合实现:软硬件综合是将高层次的软硬件描述转化为低层次实现的过程,研究如何利用系统提供的各种资源满足性能要求。

图8:软硬件协同设计流程图

MLIR + CIRCT协同设计举例

例如设计一款AI加速器芯片

- 确定功能划分

首先,需要确定哪些功能应由硬件实现,哪些可以通过软件优化:

-

硬件实现:矩阵乘法、卷积等计算密集型操作。这些操作通常需要高并行度和低延迟,因此适合通过专用硬件来实现;

-

软件优化:算法调度、数据预处理等。这些功能相对灵活,可以通过软件进行动态调整和优化,以适应不同的输入数据和计算需求;

- 并行开发与接口设计

根据上述任务划分,硬件和软件可以并行开发。此时需要定义软硬件接口,如:

-

软件实现的API:这些API用于调用硬件加速功能,并管理数据流;

-

软件实现的调度与管理接口:负责调度计算任务,管理资源分配;

-

硬件实现的总线和数据传输协议:定义数据在硬件模块之间的传输方式,以及控制信号的格式;

- 编译与转换流程

在这一阶段,使用MLIR和CIRCT进行代码转换: 注:转换流程图可以参考CIRCT发展历程章节中的方言转换图。

-

从高级语言到MLIR:使用TensorFlow或PyTorch前端编译器,将使用Python代码实现的API、调度等功能转换为MLIR中的核心方言(如Linalg、Tensor、SCF等);

-

从MLIR到机器码的转换:类似API、调度、浮点运算等功能,可以在经过MLIR内部方言之间的转换后,再转换为机器码以供CPU、浮点运算单元等执行;

-

从MLIR到CIRCT方言:将Tensor Core中的基本运算、条件语句等转换为CIRCT内部的方言(如Handshake、ESI、HW、Seq、Comb等);

-

Verilog/SystemVerilog实现:对于由Verilog/SystemVerilog编写的总线和内存等功能,可以直接使用slang工具将其翻译为Moore方言,然后再转换为CIRCT的HW、Seq、Comb等方言;

- 仿真与验证

完成上述步骤后,可以进行仿真:

-

使用Arcilator仿真工具:对生成的RTL代码进行仿真,以验证设计是否符合预期;

-

FPGA下载与测试:将生成的RTL代码下载到FPGA上进行实际测试,以验证硬件在真实环境中的性能。

得益于MLIR的设计,MLIR与CIRCT的结合是软硬件协同设计领域的一次革命性突破。通过提供一个高效的软硬件协同设计平台和高效的硬件设计能力,MLIR与CIRCT使得开发者能够快速设计和实现高性能的AI加速器芯片。这种平台能够有效地减少设计周期,提高设计质量和性能。

总结

MLIR提供了灵活且可扩展的编译基础设施,使不同领域的编译器能够共享和重用组件。CIRCT项目把MLIR应用于EDA领域,开发了一系列的RTL仿真与验证工具,不仅提升了设计的灵活性,还能缩短研发周期。总之,基于MLIR的CIRCT项目有望让芯片敏捷开发与定制化设计成为现实。

参考资料:

[1] Applying Circuit IR Compilers and Tools (CIRCT) to ML Applications

[2] Arcilator: Fast and cycle-accurate hardware simulation in CIRCT

[3] CIRCT官方文档

[4] MLIR官方文档

[5] The Golden Age of Compiler Design in an Era of HW/SW Co-design by Dr. Chris Lattner